N-Linx HR6420 高分辨率数据采集卡

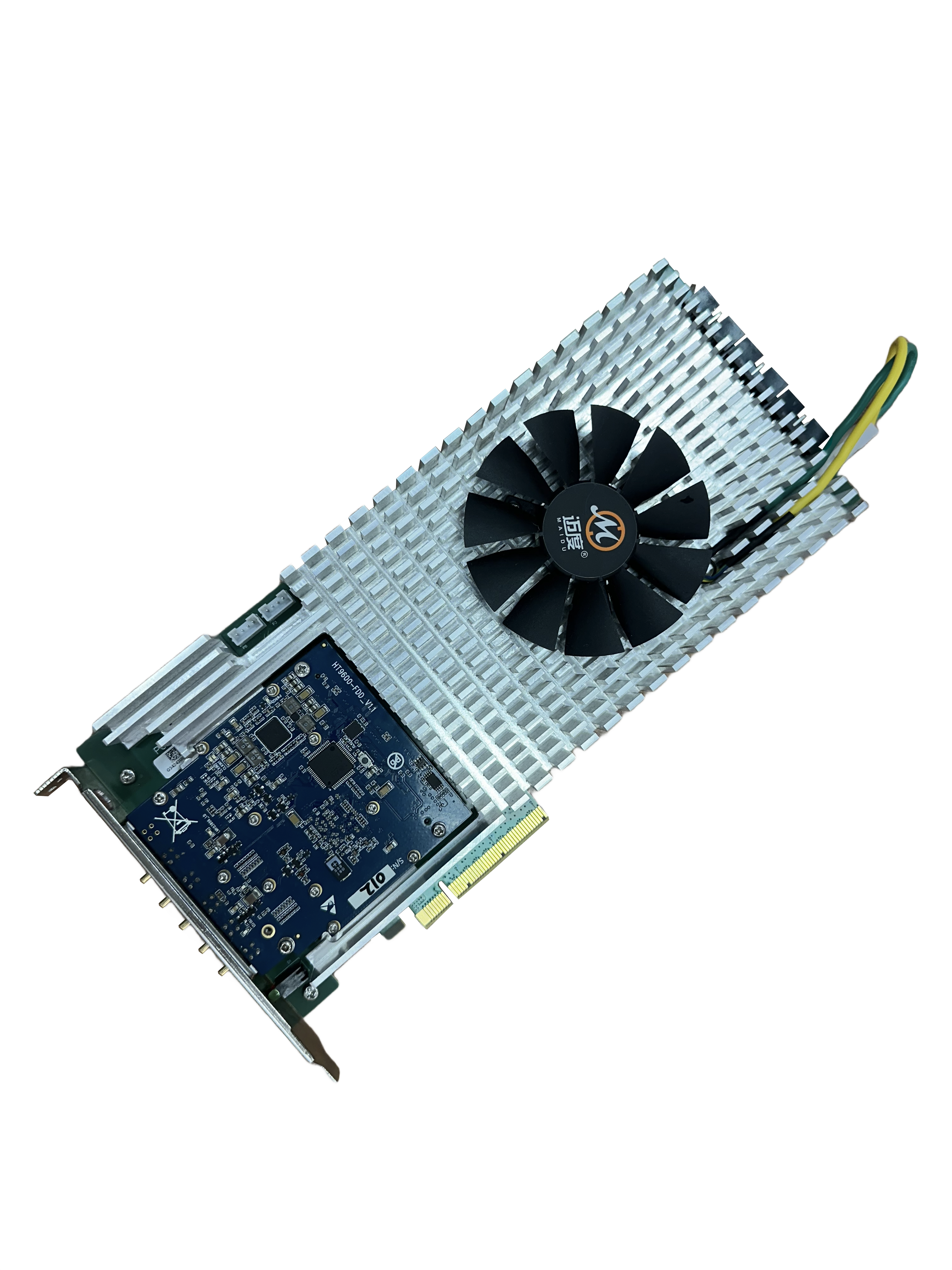

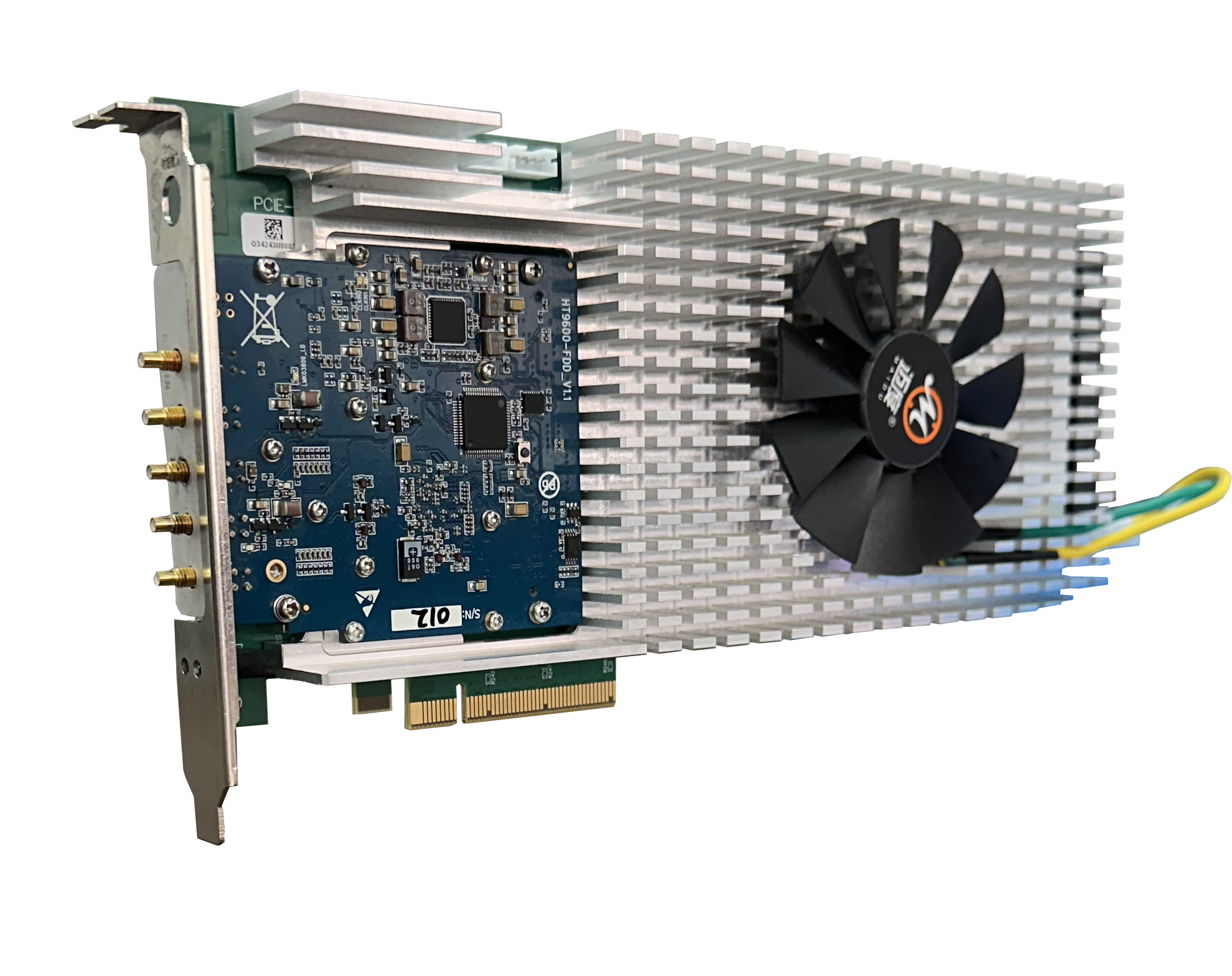

N-Linx HR6420是一款集成2通道ADC采集和4通道DAC回放的FMC板卡。其ADC(ADS54J60)具有最高1.0 GSPS的转换速率,位数为16bit;DAC(DAC39J84IAAV)则支持最高2.8 GSPS的转换速率,同样为16bit。该板卡支持可选的触发输出/触发输入功能,并提供触发和同步选项。采样时钟方面,HR6420支持内部参考时钟、外部参考时钟和外部采样时钟三种选择,时钟源选择可通过两个FPGA控制的IO信号实现,多个板卡能够通过同步信号和输出的采样时钟实现同步。

HR6420的电气与机械设计遵循FMC标准(ANSI/VITA 57.1),支持导冷,以满足用户在特殊环境下的使用需求。该板卡通过高密度连接器(HPC)与FPGA载板相连,前面板可装配9个SSMC同轴连接器,兼容坤驰科技的多种FPGA载板,如QT7010、QT7011、QT7020、QT3011,以及Xilinx和Altera等通用载板,支持高性能的算法计算。

;咨询电话: 13927489205

N-Linx HR6420是一款高性能的FMC子板,集成了2通道ADC采集和4通道DAC回放功能。它设计用于满足对高速数据采集和处理的严苛需求,广泛应用于通信、雷达、成像、科学研究等领域。该板卡具备以下主要规格和性能指标:

一、主要规格

- 连接器配置:支持7个或9个SSMC连接器,其中包括:

- 2个模拟信号DC耦合输入(AD0/1)

- 2个模拟信号DC耦合输出(DA0/1)

- 2个模拟信号AC耦合输出(AC0/1)

- 1个外部参考/采样时钟输入(CLK)

- 1个触发/同步输入(SYN)

- 1个触发输入/输出(TRG)

- ADC采样频率:16位,1.0 GSPS

- DAC采样频率:16位,2.8 GSPS

- 数据接口:ADC输出和DAC输入均符合JESD204B标准

- 兼容性:完全符合VITA 57.1规范,包括结构件、子卡尺寸、面板连接器及器件限高,大大提高了子卡的通用性和适配性

- 散热方式:提供风冷或导冷两种散热方案

- 时钟选择:内部时钟和外部时钟均可由载板控制,灵活便捷

- 连接器类型:采用HPC高引脚数连接器

- 工作温度范围:商业级0℃~+55℃,工业级-20℃~+65℃

二、性能与指标

模拟输入

- 输入耦合方式:直流耦合

- 输入通道数:2路

- 全量程输入幅度:1.9 Vpp

- 全功率带宽:1200 MHz

- 输入阻抗:50 Ohm

- 连接器:SSMC

模数转换器(ADC)

- 单芯片:双通道

- 分辨率:16bit

- 最大采样率:1.0 GSPS

- 输出兼容:JESD204B子类1

模拟输出

- 输出耦合方式:2通道AC耦合 + 2通道DC耦合

- 输出通道数:4路

- 输出幅度:-0.5 V ~ +0.6 V

- 满量程电流:10~30 mA

- 输出阻抗:50 Ohm

- 连接器:SSMC

数模转换器(DAC)

- 单芯片:4通道

- 分辨率:16bit

- 最大采样率:2.8 GSPS

- 输入兼容:JESD204B子类1

时钟

- 支持内部参考时钟:10 MHz

- 支持外部参考时钟:10-250 MHz,0 dBm ~ +8 dBm

- 支持外部时钟:最高1000 MHz,0 dBm ~ +8 dBm

- 输入阻抗:50 Ohm

- 耦合方式:交流耦合

- 连接器:SSMC

触发

- 外部触发输入:3.3V LVCMOS或LVTTL

- 触发输出:3.3V LVCMOS或LVTTL

- 最大频率:200 MHz

- 连接器:SSMC

FMC接口

- HPC: ASP-134488-01

- DP_M2C/C2M(0-7),LVDS

- LA(00-26),LVDS或LVCMOS或LVTTL

- CLK(GBTCLK0-1,CLK0-1),LVDS

功耗

- +12V: <0.6A

- +3.3V: <0.5A

- Vadj: <0.2A

三、综合性能

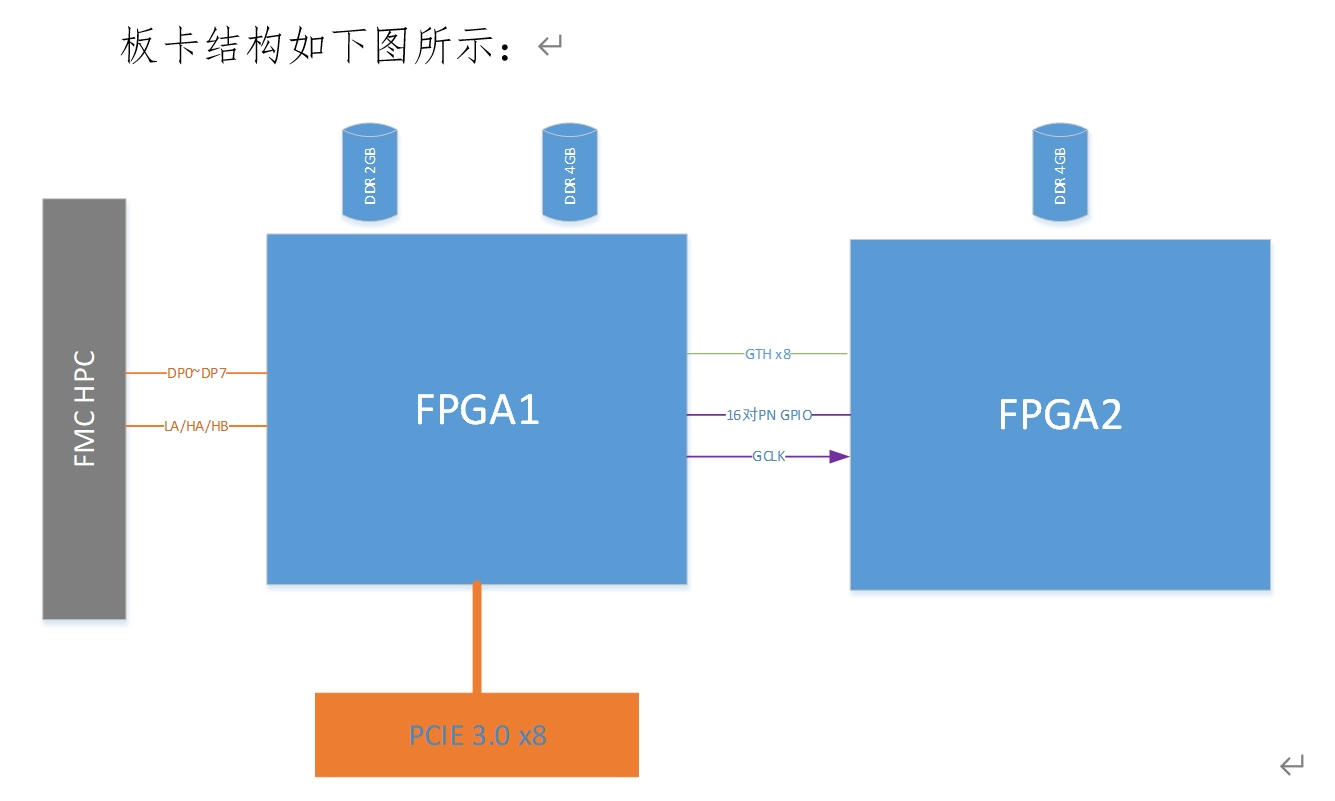

N-Linx HR6420以其强大的采样率和高分辨率,能够满足现代高性能信号处理的需求。此外,该板卡采用PCIe 3.0 x8接口,板载两片XCKU115 FPGA,支持1个FMC(HPC)接口,为用户提供更高的处理能力和灵活性。每片FPGA配备64位DDR4 SDRAM内存,确保高速数据的实时处理和存储,增强了系统的整体性能。

HR6420的设计考虑到了散热和可靠性,提供风冷和导冷选项,能够适应各种应用环境。同时,强大的时钟选择功能和多种连接器配置,使得该板卡在各种复杂应用中均能轻松适应,为用户提供极大的便利和灵活性。

关注官方微信

关注官方微信